8+0/7+1/6+2 Dual Output Digital Multi-Phase Controller

# FEATURES

- Ultra Low Quiescent Power Dual output 8 phase (8+0/7+1/6+2) PWM Controller

- Intel<sup>®</sup> VR12 Rev 1.7, VR12.5 Rev 1.5, IMVP8 Rev 1.2, AMD SVI2 Rev 1.06 & Memory VR modes

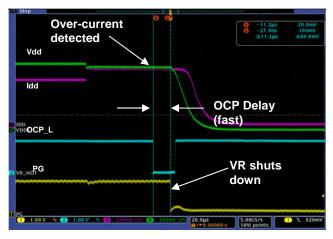

- Fast Overcurrent Flag output to warn CPU/GPU of VR overcurrent condition

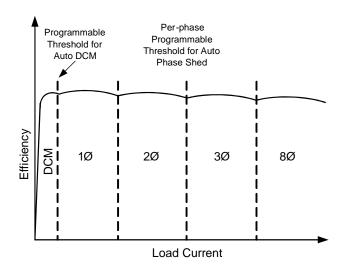

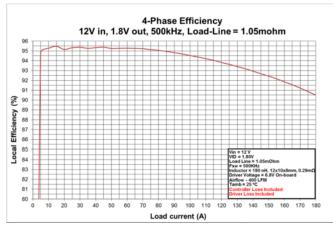

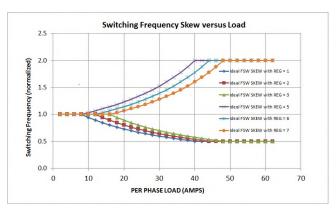

- IR Efficiency Shaping Features including Dynamic Phase Control and Automatic Power State Switching

- Programmable 1-phase or 2-phase operation for Light Loads and Active Diode Emulation for very Light Loads

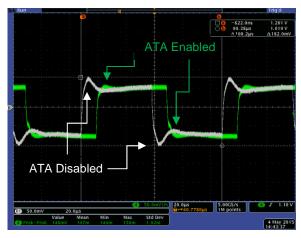

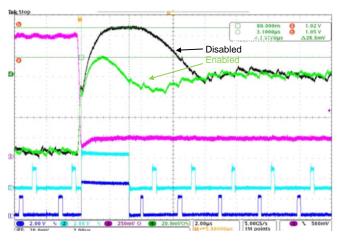

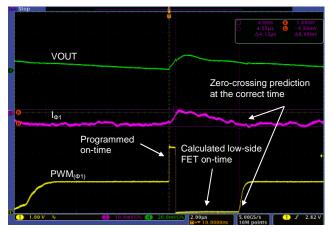

- IR Adaptive Transient Algorithm (ATA) on both loops minimizes output bulk capacitors and system cost

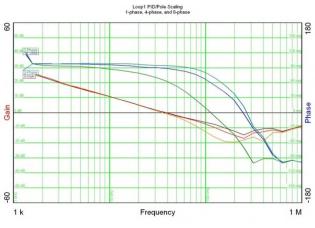

- Auto-Phase Detection with PID Coefficient autoscaling

- Fault Protection: OVP, UVP, OCP, OTP, CATFLT

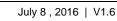

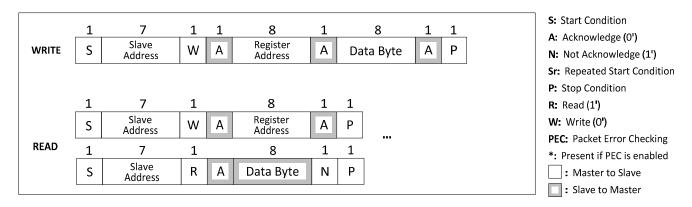

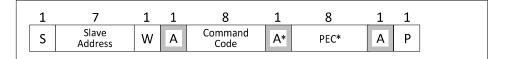

- I2C/SMBus/PMBus system interface for reporting of Temperature, Voltage, Current & Power telemetry for both loops

- Multiple Time Programming (MTP) with integrated charge pump for easy non-volatile programming

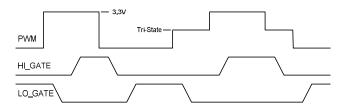

- Compatible with 3.3V tri-state drivers

- +3.3V supply voltage; -40°C to 85°C ambient operation; -40°C to 125°C junction

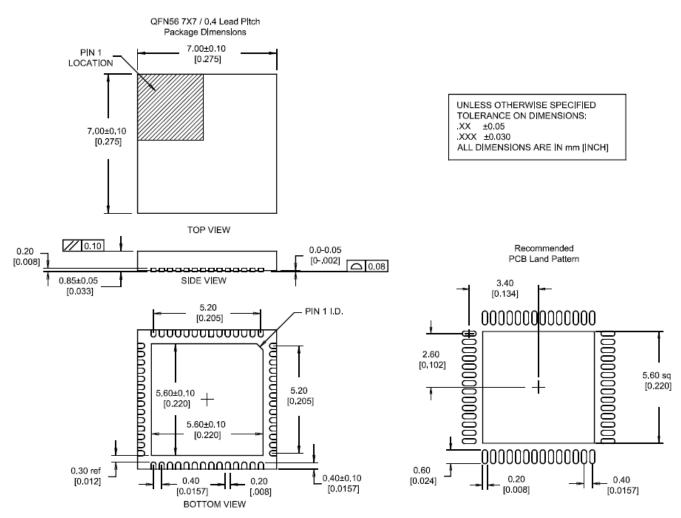

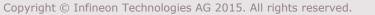

- Pb-Free, RoHS, 7x7mm 56-pin, 0.4mm pitch QFN

# **APPLICATIONS**

- Intel® VR12, VR12.5 and IMVP8 (overclocking only), AMD SVI2 based systems

- High End Desktop CPU and GPU VR

ORDERING INFORMATION

High Performance Graphics Processors, Memory VR

# DESCRIPTION

The IR35217 is a dual-loop digital multi-phase buck controller designed for CPU and GPU voltage regulation, and is fully compliant with Intel<sup>®</sup> VR12 Rev 1.7, VR12.5 Rev 1.5, IMVP8<sup>2</sup> Rev 1.2, and AMD SVI2 REV 1.06 specifications.

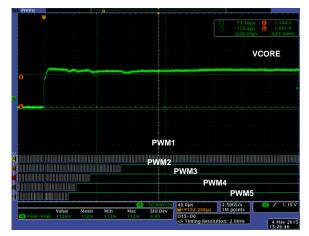

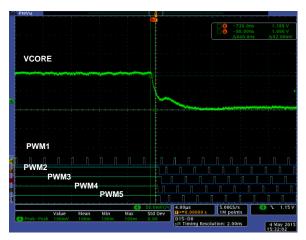

The IR35217 includes IR's Efficiency Shaping Technology to deliver exceptional efficiency at minimum cost across the entire load range. IR's Dynamic Phase Control adds/drops phases based upon load current. The IR35217 can be configured to enter 1 or 2-phase PS1 operation and active diode emulation mode automatically or by command.

IR's unique Adaptive Transient Algorithm (ATA), based on proprietary non-linear digital PWM algorithms, minimizes output bulk capacitors.

IR35217 has 127 possible address values for both the PMBus and I2C bus interfaces. The device configuration can be easily defined using the IR PowIRCenter GUI, and is stored in the on-chip Non-Volatile Memory (NVM). This reduces external components and minimizes the package size.

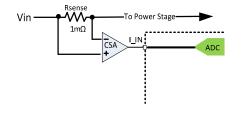

The IR35217 provides extensive OVP, UVP, OCP, OTP & CATFLT fault protection, and includes thermistor based temperature sensing or per phase temperature reporting when using the IR PowIRstage. The controller is designed to work with either Rdson current sense PowIRstages or with DCR current sense.

The IR35217 also includes numerous VR design simplifying and differentiating features, like register diagnostics, which enable fast time-to-market.

#### Standard Pack Base Part Orderable Package Type Number Part Number Form Quantity IR35217 3000 56-pin, QFN 7 mm x 7 mm Tape and Reel IR35217MxxyyTRP<sup>1</sup> IR35217 56-pin, QFN 7 mm x 7 mm Tape and Reel 3000 IR35217MTRPBF IR35217 4900 IR35217MTYPBF 56-pin, QFN 7 mm x 7 mm Tray

Notes:

1. Customer Specific Configuration File, where xx = Customer ID and yy = Configuration File (Codes assigned by IR Marketing)

2. IR35217 is not intended for application where Ultra-Low Power PS4 shutdown functionality is required..

# **ORDERING INFORMATION**

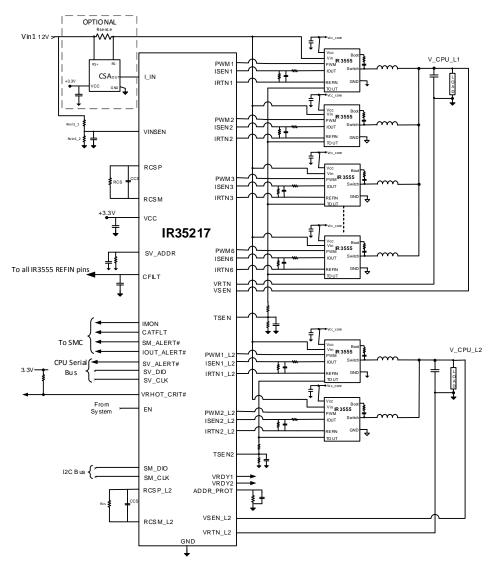

Figure 1: IR35217 Pin Diagram

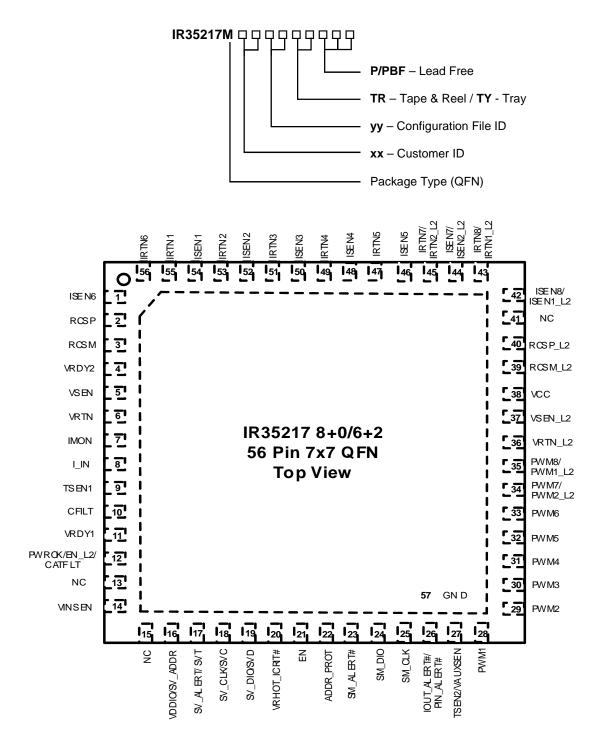

#### FUNCTIONAL BLOCK DIAGRAM

## 8+0/7+1/6+2 Dual Output Digital Multi-Phase Controller

# IR35217

Figure 2: IR35217 Block Diagram

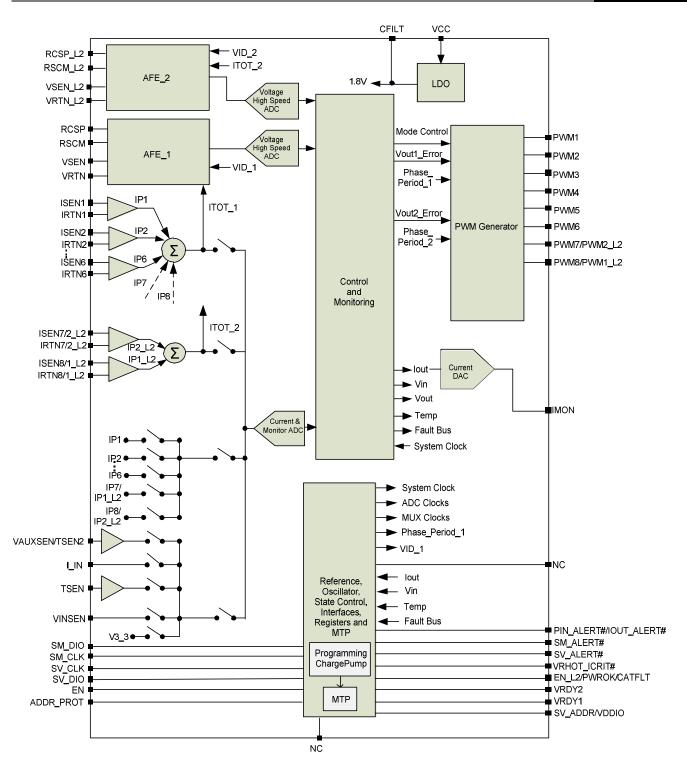

# **TYPICAL APPLICATION DIAGRAM**

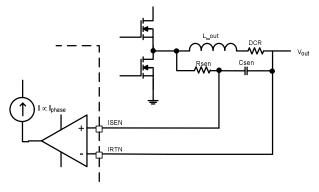

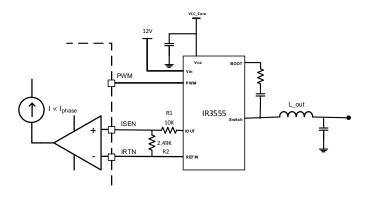

Figure 3: VR using IR35217 Controller and IR3555 PowIR Stage in 6+2 Configuration

# **PIN DESCRIPTIONS**

| PIN# | PIN NAME                   | TYPE            | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|------|----------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | ISEN6                      | A [I]           | Phase 6 Current Sense Input. Phase 6 sensed current input (+).GND if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

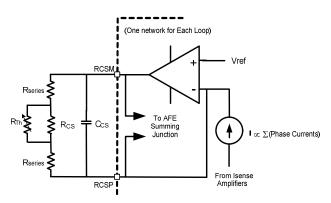

| 2    | RCSP                       | A [O]           | <b>Resistor Current Sense Positive.</b> This pin is connected to an external network to set the load line slope, bandwidth and temperature compensation for Loop 1.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3    | RCSM                       | A [O]           | <b>Resistor Current Sense Minus.</b> This pin is connected to an external network to set the load line slope, bandwidth and temperature compensation for Loop 1.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

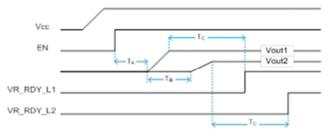

| 4    | VRDY2                      | D [O]           | <b>Voltage Regulator Ready Output (Loop #2).</b> Open-drain output that asserts high when the VR has completed soft-start to Loop #2 boot voltage. Pull-up to an external voltage through a resistor.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

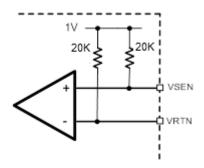

| 5    | VSEN                       | A [I]           | Voltage Sense Input. This pin is connected directly to the VR output voltage of Loop #1 at the load and should be routed differentially with VRTN.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 6    | VRTN                       | A [I]           | Voltage Sense Return Input. This pin is connected directly to Loop#1 ground at the load and should be routed differentially with VSEN.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

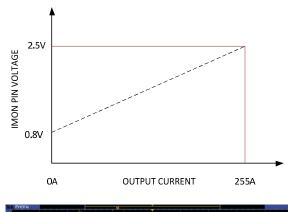

| 7    | IMON                       | A [O]           | <b>Output Current Monitor.</b> This pin puts out an analog output voltage corresponding to average output current. $0.8V = 0$ load, $2.5V = 255A$ . The maximum current for this pin is +/- 100uA. An output capacitor on this pin is not required but if a capacitor is used, its value must be limited to a maximum of 1nF.                                                                                                                                                                                                                                |  |  |  |

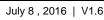

| 8    | I_IN                       | A [I]           | <b>I in.</b> Input current signal that ranges from 0 to 1.25Vdc. Used for applications that require an external input current measurement to drive the PIN ALERT# output pin and SVID input Power reporting register                                                                                                                                                                                                                                                                                                                                         |  |  |  |

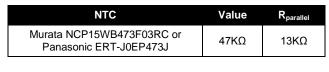

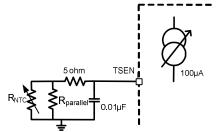

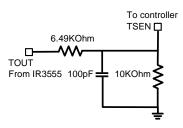

| 9    | TSEN1                      | A [I]           | <b>Temperature Sense Input Loop 1.</b> An NTC network or the temperature reporting output from an IR PowIRstage can be connected to this pin to measure temperature for VRHOT and OTP shutdown. When connected to the IR PowIRstage's temperature output; the scaled input voltage to the controller needs to be at a gain of 4.88mV per degC and an offset of 0.365 Vdc so the controller can correctly report temperature. Typically a 10kohm and 6.39kohm resistive divider is used to accomplish the scaling between the power stage and the controller. |  |  |  |

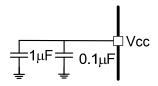

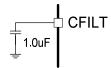

| 10   | CFILT                      | A [O]           | <b>1.8V Decoupling.</b> A $1\mu$ F capacitor on this pin provides decoupling for the internal 1.8V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 11   | VRDY1                      | D [O]           | Voltage Regulator Ready Output (Loop #1). Open-drain output that asserts high when the has completed soft-start to Loop #1 boot voltage. Pull-up to an external voltage through a resistor.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

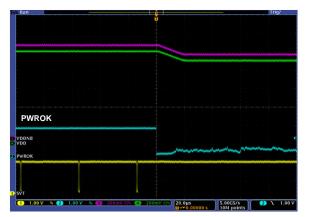

|      |                            |                 | <b>Power OK Input (AMD).</b> An input that when low indicates to return to the Boot voltage and when high indicates to use the SVI bus.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 12   | PWROK/<br>EN_L2/<br>CATFLT | D [I]           | <b>VR Enable for Loop 2.</b> When configured, ENABLE for Loop 2 is an active high system input to power-on Loop 2, provided Vin and Vcc are present. ENABLE is not pulled up on the controller. When ENABLE is pulled low, the controller de-asserts VR READY2 and shuts down loop 2 only.                                                                                                                                                                                                                                                                   |  |  |  |

|      |                            |                 | <b>Catastrophic Fault Output Pin.</b> This pin may be used as a Catastrophic Fault CMOS Output Pin that is driven to VCC under output OVP, NVM CRC errors or a TSENx fault input.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 13   | NC                         |                 | Do Not Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

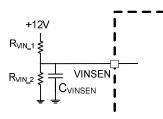

| 14   | VINSEN                     | A [I]           | <b>Voltage Sense Input.</b> This is used to detect and measure a valid input supply voltage (typically 4.5V-13.2V) to the VR.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 15   | NC                         |                 | Do Not Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 16   | VDDIO/<br>SV_ADDR          | A [P]/<br>A [I] | <b>VDDIO Input (AMD).</b> This pin provides the voltage to which the SVT line and the SVD Acknowledge are driven high.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

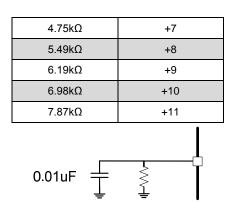

|      | SV_ADDK                    | ΛIJ             | SVID Address Input (INTEL). A resistor to ground on this pin defines the SVID address which is latched when Vcc becomes valid. Requires a 0.01µF bypass capacitor.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|      | SVT/                       |                 | SVI Telemetry Output (AMD). Telemetry and VOTF information output by the IR35217                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 17   | SV_ALERT#                  | D [O]           | Serial VID ALERT# (INTEL). SVID ALERT# is pulled low by the controller to alert the CPU of new VR12/12.5/IMVP8 Status. Pull-up to an external voltage through a resistor.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

# 8+0/7+1/6+2 Dual Output Digital Multi-Phase Controller

# IR35217

| 19         SV_DIO         D [B]         slave/s and receives data back.           20         VRHOT_ICRIT#         D [O]         VRHOT_ICRIT# D [O]         VRHOT_ICRIT# Output. Active low alert pin that can be programmed to assert if themperature resistor.           21         EN         D [I]         PR nable Input. ENABLE is used to power-on the regulator, provided Vin and Voc are preserved them an active high or an active low configuration. ENABLE pin cannot be left fleating. ENA           22         ADDR_PROT         D [B]         Bus Address & 12C Bus Protection. A resistor to ground on this pin sets the offset to the NV-value of the 12C address if configured to do so. Subsequenty, this pin becomes a logic input.           23         SM_ALERT#         D [O]         SMBus/PMBus Alert Line. Active low alert pin to indicate that the regulator status has chang Requires a pul-up. Ground if not used.           24         SM_DIO         D [B]         Serial Data Line VO. 12C/SMBus/PMBus bicdirectional serial data line. Ground in tor used.           25         SM_CLK         D [I]         Serial Clock Line Input. LIX/SMBus/PMBus clock input. The interface is rated to 1 MHz. Ground in not used.           26         IOUT_ALERT#         D [O]         Serial Clock Line Input. Active low alert pin that can be programmed to assert if the input pow exceeds a user defined threshold. Pul-up to an external voltage through a resistor.           27         TSEN2         A [I]         A [I]         NCH_ALERT# Output. Active low alert pin that ca                                                                                                                                                                                                                         | PIN#    | PIN NAME     | TYPE   | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                               |  |                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19         SV_DIO         D [B]         slave/s and receives data back.           20         VRHOT_ICRIT#         D [O]         VRHOT_ICRIT# descent suce data back.           21         EN         D [O]         VRHOT_ICRIT# descent suce data back.           21         EN         D [I]         Frankle Eis not pulled up in the controller. The polarity of the chip enable function is bit-Settaback.           21         EN         D [I]         Exact CB controller the controller. The polarity of the chip enable function is bit-Settaback.           22         ADDR_PROT         D [B]         Exact CB controller the controller. The polarity of the chip enable function is bit-Settaback.           23         SM_ALERT#         D [O]         SMBus/PMBus Alert Line. Active low alert pin to indicate that the regulator status has chang Requires a pull-up. Ground if not used.           24         SM_DIO         D [B]         Serial Clock Line Input. I2C/SMBus/PMBus bicdirectional serial data line. Ground if not used.           26         SM_CLK         D [I]         If not used.         If not used.           27         TSEN2         A [II]         PIN_ALERT#         D [O]         Imparture Same Sing LLoog 24. ANTC network or the temperature reporting output for an external voltage through a resistor.           28         SM_CLK         D [II]         Imparture Same Sene Input Loog 24. ANTC network or the temperature reporting outp                                                                                                                                                                                                                                                                                                                                            | 18      |              | D [I]  | Serial VID Clock Input. Clock input driven by the CPU Master.                                                                                                                                                                                                                                                                                 |  |                                                                                                                                                                                                    |

| 20         VRHOT_ICRIT#         D [0]         average load current exceeds user-definable thresholds. Pull-up to an external voltage throug           21         EN         D [1]         VR Enable Input. ENABLE Is used to power-on the regulator, provided Vin and Voc are pression.           22         ADDR_PROT         D [1]         Image: the imput. ENABLE is not put of the input should be index on active low configuration. ENABLE pin cannot be left floating. ENA provided Vin and Voc are pression in must be pulled up in the configuration. ENABLE pin cannot be left floating. ENA provide Vin and Voc are pression.           22         ADDR_PROT         D [8]         Bus Address & I2C Bus Protection. A resistor to ground on the pin bestore and log in put in the pin becomes a logic input in enable of dates if configured to do so. Subsequently, this pin becomes a logic input in the out of mouse be pulled be ommunication on the I2C Dus when protection is enabled. Requires a 0.01 to ground for notes filtering.           23         SM_ALERT#         D [0]         Bus Address if Active low alert pin to indicate that the regulator status has chang Requires a pull-up. Ground if not used.           24         SM_DIO         D [8]         Serial Clock Line Input. I2C/SMBus/PMBus clock input. The interface is rated to 1 MIz. Ground if not used.           25         SM_CLK         D [1]         Serial Clock Line Input. I2C/SMBus/PMBus clock input. The interface is seried.           26         IOUT_ALERT#/         D [0]         In ALERT# Output. Active low alert pin that can be programmed to assert if the input powi                                                                                                                                                  | 19      |              | D [B]  | <b>Serial VID Data I/O.</b> Is a bi-directional serial line over which the CPU Master issues commands to slave/s and receives data back.                                                                                                                                                                                                      |  |                                                                                                                                                                                                    |

| 21         EN         D [I]         ENABLE is not pulled up in the controller. The polarity of the chip enable function is bit-settable pin must be pulled high or low.           22         ADDR_PROT         D [I]/         ENABLE is not pulled wigh or low.           22         ADDR_PROT         D [I]/         Bits Address & IC2 Bus Protection. A resistor to ground on this pin sets the offset to the NV value of the I2C address if configured to do so. Subsequently, this pin becomes a logic input value of the I2C address if configured to do so. Subsequently, this pin becomes a logic input value of the I2C address if configured to do so. Subsequently, this pin becomes a logic input value of the I2C address if configured to do so. Subsequently, this pin becomes a logic input value of the I2C address if configured to a so. Subsequently, this pin becomes a logic input value of the I2C address if configured to a so. Subsequently, this pin becomes a logic input value of the I2C address if configured to a so. Subsequently, this pin becomes a logic input value of the I2C address if configured to a so. Subsequently, this pin becomes a logic input value of the I2C address if configured to a so. Subsequently, this pin becomes a logic input value of the logic address if configured to a so. Subsequently, the pin value of the subset of the I2C address if configured to a so. Subsequently, the prove result of the I2C address if configured to a so. Subsequently, the pin value of the I2C address if configured to a so. Subsequently, the pin become support to a set if the output of the tot used.           26         SM_LLET##         D [0]         Find LERT#         D [0]         Find LERT#         D [0]         Find LERT#         D [0]           27                | 20      | VRHOT_ICRIT# | D [O]  | VRHOT_ICRIT# Output. Active low alert pin that can be programmed to assert if temperature or average load current exceeds user-definable thresholds. Pull-up to an external voltage through a resistor.                                                                                                                                       |  |                                                                                                                                                                                                    |

| 22         ADDR_PROT         D [B]/         Bus Address & 12C Bus Protection. A resistor to ground on this pin becomes a logic input to value of the 12C address if configured to do so. Subsequently, this pin becomes a logic input to enable of disable communication on the 12C bus when protection is enabled. Requires a 0.01 to ground for noise filtering.           23         SM_ALERT#         D [O]         SMBus/PMBus Alert Line. Active low alert pin to indicate that the regulator status has chang Requires a pull-up. Ground if not used.           24         SM_DIO         D [B]         Serial Data Line I/O. 12C/SMBus/PMBus bi-directional serial data line. Ground if not used.           25         SM_CLK         D [I]         Serial Clock Line Input. 12C/SMBus/PMBus clock input. The interface is rated to 1 MHz. Gro if not used.           26         IOUT_ALERT#/<br>PIN_ALERT#         D [O]         IOUT_ALERT#Output. Active low alert pin that can be programmed to assert if the output current exceeds user-defined threshold. Pull-up to an external voltage through a resistor.           27         TSEN2<br>/VAUXSEN         A [I]         Timearture Sense Input Loop #2. An NTC network or the temperature reporting output for an IR PowiRstage can be connected to this pin to masure temperature for VRHOT. Float if not used.           28 - 33         PWM1 – PWM6         A [O]         Phase 1-6 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.           34         PWM7/<br>PWM2_L2         A [O                                                                                                                                | 21      | EN           | D [I]  | VR Enable Input. ENABLE is used to power-on the regulator, provided Vin and Vcc are present.<br>ENABLE is not pulled up in the controller. The polarity of the chip enable function is bit-settable to<br>either an active high or an active low configuration. ENABLE pin cannot be left floating. ENABLE<br>pin must be pulled high or low. |  |                                                                                                                                                                                                    |

| 23       SM_ALERT#       D101       Requires a pull-up. Ground if not used.         24       SM_DO       D [B]       Serial Data Line V0. 12C/SMBus/PMBus bi-directional serial data line. Ground if not used.         25       SM_CLK       D [I]       Serial Data Line V0. 12C/SMBus/PMBus clock input. The interface is rated to 1 MHz. Gro<br>if not used.         26       IOUT_ALERT#/<br>PIN_ALERT#       D [O]       Serial Clock Line Input. 12C/SMBus/PMBus clock input. The interface is rated to 1 MHz. Gro<br>if not used.         27       TSEN2<br>/VAUXSEN       D [O]       IOUT_ALERT# Output. Active low alert pin that can be programmed to assert if the output<br>current exceeds user-defined threshold. Pull-up to an external voltage through a resistor.         28 - 33       PWM1 - PWM6       A [D]       Temperature Sense Input Loop #2. An NTC network or the temperature for VRHOT. Float if no<br>used.         28 - 33       PWM1 - PWM6       A [D]       Temperature Sense Input Loop #2. An NTC network or the temperature for VRHOT. Float if no<br>used.         34       PWM7/<br>PWM2_L2       A [D]       Phase 1-6 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input<br>an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes<br>active. Float if not used.         35       PWM8/<br>PWM8/<br>PWM8/<br>PWM8/<br>36       A [O]       Phase 1 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input<br>an external MOSFET gate driver. The power-up state is high-impedance until ENABLE<br>goes active.         <                                                                                                                                                                                     | 22      | ADDR_PROT    | D [B]/ | Bus Address & I2C Bus Protection. A resistor to ground on this pin sets the offset to the NVM value of the I2C address if configured to do so. Subsequently, this pin becomes a logic input to enable or disable communication on the I2C bus when protection is enabled. Requires a $0.01 \mu$ F                                             |  |                                                                                                                                                                                                    |

| 25         SM_CLK         D [I]         Serial Clock Line Input. I2C/SMBus/PMBus clock input. The interface is rated to 1 MHz. Gro<br>if not used.           26         IOUT_ALERT#/<br>PIN_ALERT#         D [O]         IOUT_ALERT#/<br>PIN_ALERT#         D [O]           27         TSEN2<br>/VAUXSEN         A [I]         IOUT_ALERT#Output. Active low alert pin that can be programmed to assert if the output<br>current exceeds user-defined threshold. Pull-up to an external voltage through a resistor.           27         TSEN2<br>/VAUXSEN         A [I]         Temperature Sense Input Loop #2. An NTC network or the temperature reporting output fro<br>an IR PowIRstage can be connected to this pin to measure temperature for VRHOT. Float if no<br>used.           28 - 33         PWM1 – PWM6         A [O]         Phase 1-6 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input<br>active. Float if not used.           34         PWM7/<br>PWM2_L2         A [O]         Phase 7 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input<br>active. Float if not used.           35         PWM8/<br>PWM8/<br>PWM8/<br>PWM1_L2         A [O]         Phase 7 Pulse Width Modulation Outputs. PWM signal pin which is connected to the<br>input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes<br>active. Float if not used.           36         VRTN_L2         A [O]         Phase 1 Pulse Width Modulation Outputs. PWM signal pin which is connected to the<br>input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE<br>goes active.                                                                                                                                     | 23      | SM_ALERT#    | D [O]  | <b>SMBus/PMBus Alert Line.</b> Active low alert pin to indicate that the regulator status has changed. Requires a pull-up. Ground if not used.                                                                                                                                                                                                |  |                                                                                                                                                                                                    |

| 25       SM_LCLK       D [I]       if not used.         26       IOUT_ALERT#/<br>PIN_ALERT#       D [O]       if not used.         27       TSEN2<br>/VAUXSEN       D [O]       IDUT_ALERT# Output. Active low alert pin that can be programmed to assert if the output<br>exceeds a user defined threshold. Pull-up to an external voltage through a resistor.         27       TSEN2<br>/VAUXSEN       A [I]       Temperature Sense Input Loop #2. An NTC network or the temperature reporting output fro<br>an IR PowIRstage can be connected to this pin to measure temperature for VRHOT. Float if n<br>used.         28 - 33       PWM1 – PWM6       A [O]       Temperature Sense Input Loop #2. An NTC network or the temperature reporting output fro<br>an IR PowIRstage can be connected to this pin to measure temperature for VRHOT. Float if not<br>used.         28 - 33       PWM1 – PWM6       A [O]       Phase 1-6 Pulse Width Modulation Outputs. PVM signal pin which is connected to the inpu<br>an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes<br>active. Float if not used.         34       PWM7/<br>PWM2_L2       A [O]       Phase 7 Pulse Width Modulation Outputs. PVM signal pin which is connected to the input<br>an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes<br>active. Float if not used.         35       PWM8/<br>PWM1_L2       A [O]       Phase 8 Pulse Width Modulation Outputs. PVM signal pin which is connected to the<br>input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE<br>goes active.         36       VRTN_L2 <td>24</td> <td>SM_DIO</td> <td>D [B]</td> <td>Serial Data Line I/O. I2C/SMBus/PMBus bi-directional serial data line. Ground if not used.</td> | 24      | SM_DIO       | D [B]  | Serial Data Line I/O. I2C/SMBus/PMBus bi-directional serial data line. Ground if not used.                                                                                                                                                                                                                                                    |  |                                                                                                                                                                                                    |

| 26       IOUT_ALERT#/       P [O]       current exceeds user-defined threshold. Pull-up to an external voltage through a resistor.         27       TSEN2       A [I]       A [I]       A [I]         27       TSEN2       A [I]       A [I]         28 - 33       PWM1 – PWM6       A [O]       Phase 1-6 Pulse Width Modulation Outputs. PVM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         34       PWM7/       PWM2_L2       A [O]       Phase 1-6 Pulse Width Modulation Outputs. PVM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         35       PWM8/       PWM7/       PM8/       A [O]         36       VRTN_L2       A [I]       A [I]       A [I]         36       VRTN_L2       A [I]       A [I]       A [I]         37       VSEN_L2       A [I]       A [I]       A [I]         37       VSEN_L2       A [I]       A [I]       A [I]       A [I]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25      | SM_CLK       | D [I]  | Serial Clock Line Input. I2C/SMBus/PMBus clock input. The interface is rated to 1 MHz. Ground if not used.                                                                                                                                                                                                                                    |  |                                                                                                                                                                                                    |

| PIN_ALERT#       PIN_ALERT# Output.       Active low aler pin that can be programmed to assert if the input powe exceeds a user defined threshold. Pull-up to an external voltage through a resistor         27       TSEN2<br>/VAUXSEN       A [I]       Temperature Sense Input Loop #2. An NTC network or the temperature reporting output from used.         28 - 33       PWM1 – PWM6       A [O]       Temperature Voltage Sense Input. Monitors an additional power supply to ensure that both the IR35217 Vcc and other voltages (such as VCC to the driver) are operational. Float if not used.         34       PWM7/<br>PWM2_L2       A [O]       Phase 1-6 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         35       PWM8/<br>PWM1_L2       A [O]       Phase 7 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         35       PWM8/<br>PWM1_L2       A [O]       Phase 7 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         36       VRTN_L2       A [O]       Phase 8 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         36       VRTN_L2       A [I]       Vo                                                                                                                                     | 26      | IOUT_ALERT#/ |        |                                                                                                                                                                                                                                                                                                                                               |  |                                                                                                                                                                                                    |

| 27       TSEN2<br>/VAUXSEN       A [I]<br>A [I]       a IR PowlRstage can be connected to this pin to measure temperature for VRHOT. Float if n<br>used.         28 - 33       PWM1 - PWM6       A [O]       A III<br>Auxiliary Voltage Sense Input. Monitors an additional power supply to ensure that both the<br>IR35217 Vcc and other voltages (such as VCC to the driver) are operational. Float if not used         28 - 33       PWM1 - PWM6       A [O]       Phase 1-6 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input<br>an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes<br>active. Float if not used.         34       PWM7/<br>PWM2_L2       A [O]       Phase 7 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input<br>an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes<br>active. Float if not used.         35       PWM8/<br>PWM1_L2       A [O]       Phase 8 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input<br>an external MOSFET gate driver. The power-up state is high-impedance until ENABLE<br>goes active.         36       PWM8/<br>PWM1_L2       A [O]       Phase 8 Pulse Width Modulation Outputs. PVM signal pin which is connected to the<br>input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes<br>active. Float if not used.         36       VRTN_L2       A [O]       Phase 8 Pulse Width Modulation Outputs. PVM signal pin which is connected to the<br>input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE<br>goes active.         36       VRTN_L2                                                                                         | 20      | PIN_ALERT#   | D[O]   | <b>PIN_ALERT# Output.</b> Active low alert pin that can be programmed to assert if the input power exceeds a user defined threshold. Pull-up to an external voltage through a resistor                                                                                                                                                        |  |                                                                                                                                                                                                    |

| 36       VRTN_L2       A [0]       A [0]       Phase 1 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         36       VRTN_L2       A [0]       Phase 1 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         36       VRTN_L2       A [0]       Phase 3 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         36       VRTN_L2       A [0]       Phase 3 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active.         36       VRTN_L2       A [0]       Phase 3 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active.         36       VRTN_L2       A [0]       Voltage Sense Return Input Loop#2. This pin is connected directly to Loop 2 ground at the and should be routed differentially with VSEN_L2. GND if not used.         37       VSEN_L2       A [1]       Voltage Sense Input Loop#2. This pin is connected directly to the VR output voltage of Loop at the external Photom Photo                                                                                                              | 27      | 27 TSEN2 A   |        | 7                                                                                                                                                                                                                                                                                                                                             |  | <b>Temperature Sense Input Loop #2.</b> An NTC network or the temperature reporting output from an IR PowIRstage can be connected to this pin to measure temperature for VRHOT. Float if not used. |

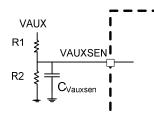

| 28 - 33       PWM1 – PWM6       A [0]       an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         34       PWM7/<br>PWM2_L2       A [0]       Phase 7 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input on external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         35       PWM8/<br>PWM1_L2       A [0]       Phase 7 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active.         35       PWM8/<br>PWM1_L2       A [0]       Phase 8 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input on external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active.         36       VRTN_L2       A [0]       Phase 8 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         36       VRTN_L2       A [0]       Voltage Sense Return Input Loop#2. This pin is connected directly to Loop 2 ground at the and should be routed differentially with VSEN_L2. GND if not used.         37       VSEN_L2       A [I]       Voltage Sense Input Loop#2. This pin is connected directly to the VR output voltage of Loop at the                                                                                                                                                                                                                                                                                                                |         | /VAUXSEN     | A [I]  | <b>Auxiliary Voltage Sense Input.</b> Monitors an additional power supply to ensure that both the IR35217 Vcc and other voltages (such as VCC to the driver) are operational. Float if not used.                                                                                                                                              |  |                                                                                                                                                                                                    |

| 34       PWM7/<br>PWM2_L2       A [O]       an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         35       PWM8/<br>PWM1_L2       A [O]       an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. The power-up state is high-impedance until ENABLE goes active.         35       PWM8/<br>PWM1_L2       A [O]       Phase 8 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active.         36       VRTN_L2       A [I]       Points a external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         36       VRTN_L2       A [I]       Voltage Sense Return Input Loop#2. This pin is connected directly to Loop 2 ground at the and should be routed differentially with VSEN_L2. GND if not used.         37       VSEN_L2       A [I]       Voltage Sense Input Loop#2. This pin is connected directly to the VR output voltage of Loop at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28 - 33 | PWM1 – PWM6  | A [O]  |                                                                                                                                                                                                                                                                                                                                               |  |                                                                                                                                                                                                    |

| 35       PWIM2_L2       Loop 2 Phase 2 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input of an external MOSFET gate driver. The power-up state is high-impedance until ENABL goes active.         35       PWIM8/       PWIM1_L2       Phase 8 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         36       VRTN_L2       A [I]       Voltage Sense Return Input Loop#2. This pin is connected directly to Loop 2 ground at the and should be routed differentially with VSEN_L2. GND if not used.         37       VSEN_L2       A [I]       Voltage Sense Input Loop#2. This pin is connected directly to the VR output voltage of Loop at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24      | PWM7/        | A [O]  | 5 1 1 5 1 5                                                                                                                                                                                                                                                                                                                                   |  |                                                                                                                                                                                                    |

| 35       PWM8/<br>PWM1_L2       A [O]       an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active. Float if not used.         36       VRTN_L2       A [I]       Voltage Sense Return Input Loop#2. This pin is connected directly to Loop 2 ground at the should be routed differentially with VSEN_L2. GND if not used.         37       VSEN_L2       A [I]       Voltage Sense Input Loop#2. This pin is connected directly to the VR output voltage of Loop at the should be routed differentially with VSEN_L2. GND if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34      | PWM2_L2      | A [U]  | <b>Loop 2 Phase 2 Pulse Width Modulation Outputs.</b> PWM signal pin which is connected to the input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active.                                                                                                                                        |  |                                                                                                                                                                                                    |

| PWIM1_L2       Loop 2 Phase 1 Pulse Width Modulation Outputs. PWM signal pin which is connected to the input of an external MOSFET gate driver. The power-up state is high-impedance until ENABL goes active.         36       VRTN_L2       A [I]       Voltage Sense Return Input Loop#2. This pin is connected directly to Loop 2 ground at the should be routed differentially with VSEN_L2. GND if not used.         37       VSEN_L2       A [I]       Voltage Sense Input Loop#2. This pin is connected directly to the VR output voltage of Loop at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 05      | PWM8/        | 4 (0)  |                                                                                                                                                                                                                                                                                                                                               |  |                                                                                                                                                                                                    |

| 36       VRTN_L2       A [I]       and should be routed differentially with VSEN_L2. GND if not used.         37       VSEN_L2       A [I]       Voltage Sense Input Loop#2. This pin is connected directly to the VR output voltage of Loop at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35      | PWM1_L2      | A [U]  | <b>Loop 2 Phase 1 Pulse Width Modulation Outputs.</b> PWM signal pin which is connected to the input of an external MOSFET gate driver. The power-up state is high-impedance until ENABLE goes active.                                                                                                                                        |  |                                                                                                                                                                                                    |

| 37 VSEN_L2 A [I] at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36      | VRTN_L2      | A [I]  |                                                                                                                                                                                                                                                                                                                                               |  |                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37      | VSEN_L2      | A [I]  | Voltage Sense Input Loop#2. This pin is connected directly to the VR output voltage of Loop 2 at the load and should be routed differentially with VRTN_L2. GND if not used.                                                                                                                                                                  |  |                                                                                                                                                                                                    |

| 38 VCC A [P] Input Supply Voltage. 3.3V supply to power the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38      | VCC          | A [P]  |                                                                                                                                                                                                                                                                                                                                               |  |                                                                                                                                                                                                    |

## 8+0/7+1/6+2 Dual Output Digital Multi-Phase Controller

| PIN#        | PIN NAME        | TYPE  | PIN DESCRIPTION                                                                                                                                                                                         |   |                     |   |       |                                                                                                                |

|-------------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------|---|-------|----------------------------------------------------------------------------------------------------------------|

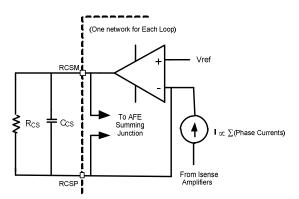

| 39          | RCSM_L2         | A [I] | <b>Resistor Current Sense Minus Loop#2.</b> This pin is connected to an external network to set the load line slope, bandwidth and temperature compensation for Loop 2. Connect 10K to RCSP if not used |   |                     |   |       |                                                                                                                |

| 40          | RCSP_L2         | A [I] | <b>Resistor Current Sense Positive Loop#2.</b> This pin is connected to an external network to set the load line slope, bandwidth and temperature compensation for Loop 2.                              |   |                     |   |       |                                                                                                                |

| 41          | NC              |       | Do Not Connect                                                                                                                                                                                          |   |                     |   |       |                                                                                                                |

| 42          | ISEN 1_L2/      | A [I] | Loop 2 Phase 1 Current Sense Input. Loop 2 Phase 1 sensed current input (+). GND if not used.                                                                                                           |   |                     |   |       |                                                                                                                |

|             | ISEN8           |       | Phase 8 Current Sense Input. Phase 8 sensed current input (+).GND if not used.                                                                                                                          |   |                     |   |       |                                                                                                                |

| 43          | IRTN 1_L2/      | A [I] | Loop 2 Phase 1 Current Sense Return Input. Loop 2 Phase 1 sensed current input return (-). GND if not used.                                                                                             |   |                     |   |       |                                                                                                                |

|             | IRTN8           |       | Phase 8 Current Sense Return Input. Phase 8 sensed current input return (-).GND if not used.                                                                                                            |   |                     |   |       |                                                                                                                |

| 44          | ISEN 2_L2/      | A [I] | Loop 2 Phase 2 Current Sense Input. Loop 2 Phase 2 sensed current input (+).GND if not used.                                                                                                            |   |                     |   |       |                                                                                                                |

| 44          | ISEN7           | A [i] | Phase 7 Current Sense Input. Phase 7 sensed current input (+).GND if not used.                                                                                                                          |   |                     |   |       |                                                                                                                |

| 45          | IRTN 2_L2/ A [I |       | —                                                                                                                                                                                                       | — | IRTN 2_L2/<br>IRTN7 | _ | A [I] | Loop 2 Phase 2 Current Sense Return Input. Loop 2 Phase 2 sensed current input return (-<br>).GND if not used. |

|             |                 |       | Phase 7 Current Sense Return Input. Phase 7 sensed current input return (-).GND if not used.                                                                                                            |   |                     |   |       |                                                                                                                |

| 46          | ISEN 5          | A [I] | Phase 5 Current Sense Input. Phase 5 sensed current input (+).GND if not used.                                                                                                                          |   |                     |   |       |                                                                                                                |

| 47          | IRTN 5          | A [I] | Phase 5 Current Sense Return Input. Phase 5 sensed current input return (-). GND if not used.                                                                                                           |   |                     |   |       |                                                                                                                |

| 48          | ISEN 4          | A [I] | Phase 4 Current Sense Input. Phase 4 sensed current input (+).GND if not used.                                                                                                                          |   |                     |   |       |                                                                                                                |

| 49          | IRTN 4          | A [I] | Phase 4 Current Sense Return Input. Phase 4 sensed current input return (-).GND if not used.                                                                                                            |   |                     |   |       |                                                                                                                |

| 50          | ISEN 3          | A [I] | Phase 3 Current Sense Input. Phase 3 sensed current input (+).GND if not used.                                                                                                                          |   |                     |   |       |                                                                                                                |

| 51          | IRTN 3          | A [I] | Phase 3 Current Sense Return Input. Phase 3 sensed current input return (-).GND if not used.                                                                                                            |   |                     |   |       |                                                                                                                |

| 52          | ISEN 2          | A [I] | Phase 2 Current Sense Input. Phase 2 sensed current input (+).GND if not used.                                                                                                                          |   |                     |   |       |                                                                                                                |

| 53          | IRTN 2          | A [I] | Phase 2 Current Sense Return Input. Phase 2 sensed current input return (-).GND if not used.                                                                                                            |   |                     |   |       |                                                                                                                |

| 54          | ISEN 1          | A [I] | Phase 1 Current Sense Input. Phase 1 sensed current input (+).GND if not used.                                                                                                                          |   |                     |   |       |                                                                                                                |

| 55          | IRTN 1          | A [I] | Phase 1 Current Sense Return Input. Phase 1 sensed current input return (-).GND if not used.                                                                                                            |   |                     |   |       |                                                                                                                |

| 56          | IRTN6           | A [I] | Phase 6 Current Sense Return Input. Phase 6 sensed current input return (-).GND if not used.                                                                                                            |   |                     |   |       |                                                                                                                |

| 57<br>(PAD) | GND             |       | <b>Ground.</b> Ground reference for the IC. The large metal pad on the bottom must be connected to Ground.                                                                                              |   |                     |   |       |                                                                                                                |

Note 1: A - Analog; D - Digital; [I] - Input; [O] - Output; [B] - Bi-directional; [P] - Power

# **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (VCC)                                | GND-0.3V to 4.0V       |

|-----------------------------------------------------|------------------------|